《数字逻辑》课程设计

题目一:数字电子钟设计

设计任务及要求

- 任务

用计数器设计一个电子钟,显示时、分、秒。 - 要求

(1) 小时为 00-23 二十四进制计数器,分、秒为 00-59 六十进制计数器;

(2) 用八段数码管进行显示时、分、秒。

(3) 用 Logisim 画图,并进行仿真。要求能看到正确的时、分、秒信息。

(4) 先用 Logisim 软件仿真测试是否正确,再提交网站(EduCoder)测评。

实验条件

- Java Runtime Environment 环境

- Logisim虚拟数字电路仿真平台

设计过程

设计原理与思路

4位递增计数器的设计

数字电子钟的基本组成单元由4位递增计数器构成,在进行其他器件设计前,先要完成4位递增计数器的设计。

计数是一种最简单的基本运算。计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,等等。

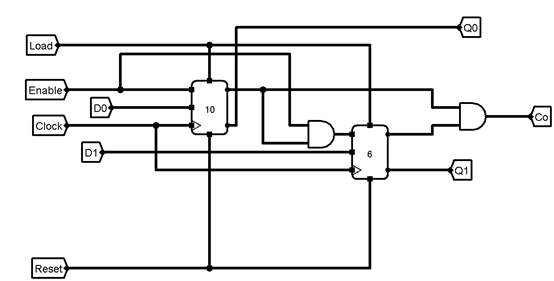

这里设计了一个带有同步置数、异步清零功能的4位同步递增计数器。

引脚说明:

| 信号 | 输入输出 | 位宽 | 说明 |

|---|---|---|---|

| Clock | 输入 | 1位 | 时钟脉冲,上升沿有效 |

| Reset | 输入 | 1位 | 异步清零端:Reset=1时,Q=0 |

| Enable | 输入 | 1位 | 使能端:Reset=0时,Enable=1递增计数、0保持 |

| Load | 输入 | 1位 | 同步置数端:Reset=0、Load=1、Clock上升沿时,Q=D |

| D | 输入 | 4位 | 并行数据加载端 |

| Q | 输出 | 4位 | 状态输出端 |

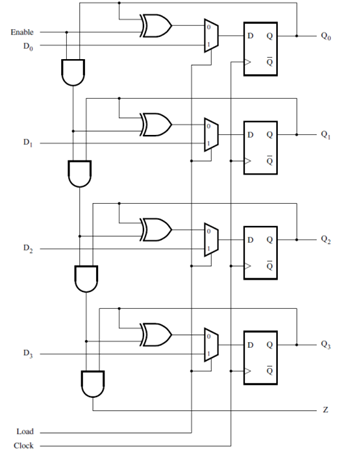

具有并行加载功能的计数器原理如下图所示:

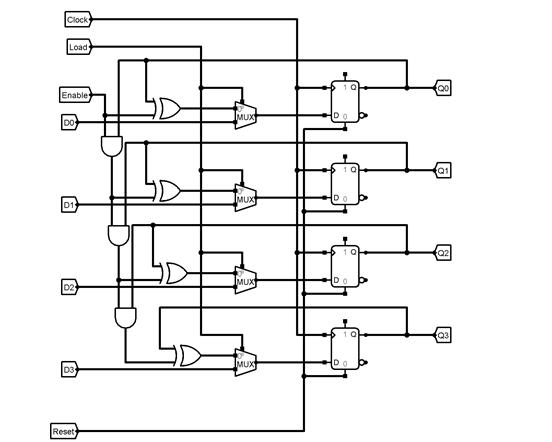

将4位递增计数器封装后的外观:

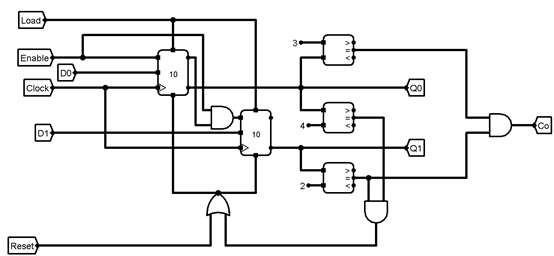

六进制计数器的设计

六进制计数器可由4位递增计数器构成,当4位递增计数器计数到6时,异步清零使Q=0,这样就完成了六进制计数器的功能。

六进制计数器是构成六十进制计数器的基础。

十进制计数器的设计

十进制计数器可由4位递增计数器构成,当4位递增计数器计数到10时,异步清零使Q=0,这样就完成了十进制计数器的功能。

十进制计数器是构成六十进制计数器的基础。

六十进制计数器的设计

六十进制计数器可由六进制计数器和十进制计数器构成,10进制计数器的进位输出端是六进制计数器的使能端(Enable)触发条件,每十次触发一次6进制计数器,而6进制计数器本身最大计数为6,这样就完成了六十进制计数器的功能。

六十进制计数器是构成数字电子钟的基础。

24进制计数器的设计

24进制计数器可由两个十进制计数器构成。

可用第一个十进制表示个位,记为计数器A。第二个十进制计数器表示十位,记为计数器B。

计数器A的进位输出端是计数器B的使能端(Enable)触发条件,每十次触发一次计数器B,同时,检测计数器A和B的状态输出端,当状态值为23时,使整个电路的进位输出端为1,当状态值为24时,异步清零,使计数器A和B的Q均为0。这样就完成了24进制计数器的功能。

24进制计数器是构成数字电子钟的基础。

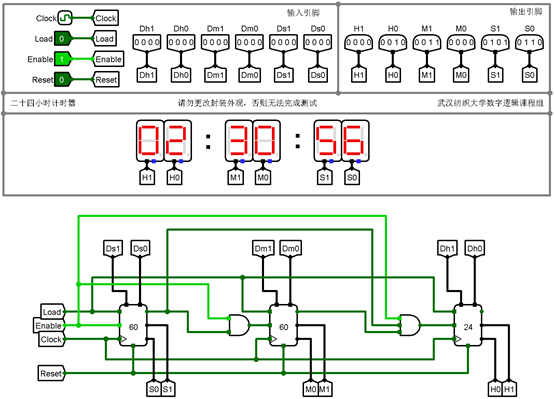

数字电子钟的设计

数字电子钟由小时(0-23)、分钟(0-59)、秒(0-60)构成。

秒由六十进制计数器构成,计数的条件是时钟的滴答。所以,在实际仿真的时候,可以调整时钟频率为1Hz,使其符合1秒1次的计数规则。

分钟由六十进制计数器构成,计数的条件是当秒钟产生进位。

小时由24进制计数器构成,计数的条件是当分钟和秒钟同时产生进位。

在实际仿真中,用16进制数字显示器件(Hex Digit Display)显示上述器件产生的状态,这样就完成了数字电子钟的功能和设计。

逻辑电路图

4位递增计数器:

六进制计数器:

十进制计数器:

六十进制计数器:

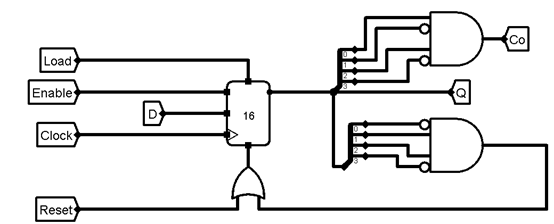

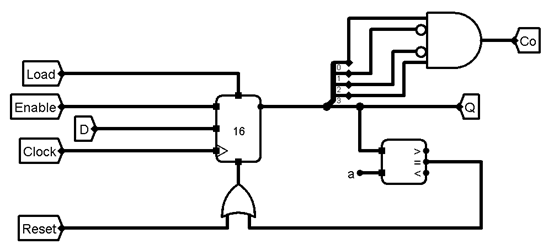

24进制计数器:

数字电子钟:

实验测试

将Clock信号,由手动点击改为时钟连续,将使能端Enable启动,然后进行测试:

题目二:路灯巡回检测器

设计任务及要求

- 任务

用 Verilog 语言设计 8 个路灯巡回检测电路。 - 要求

- 巡回检测 8 个路灯,并用 8 个 LED 灯显示好坏。路灯正常时对应的 LED 灯熄灭,路灯故障时对应的 LED 灯点亮;

- 能够迅速、准确地判出哪一个路灯坏,并用一个七段数码管显示出故障 灯的总数;

- 有启动停止开关。

- 自行绑定开发板的管脚,并下载到开发板上观察实际效果。

实验条件

- Verilog编程和EDA设计工具:Altera Quartus Ⅱ 11.0

- FPGA开发板:Altera DE2-115

设计过程

设计原理和思路

使用一个开关作为使能端,控制整个检测器的启动与停止。

当使能端关闭时,每个路灯无论其是否为故障状态,都不点亮对应的LED灯。同时,七段数码管也不点亮。

当使能端开启时,设定一个cnt作为计数器,使用always语句检测每一个路灯是否故障,如果该路灯故障,点亮对应的LED灯,并使cnt计数器(每次循环前,cnt置零)加1;如果该路灯不故障,用七段数码管hex显示cnt对应的数字。

Verilog代码

1 | module street_lamp_detector(w, hex, leds); |

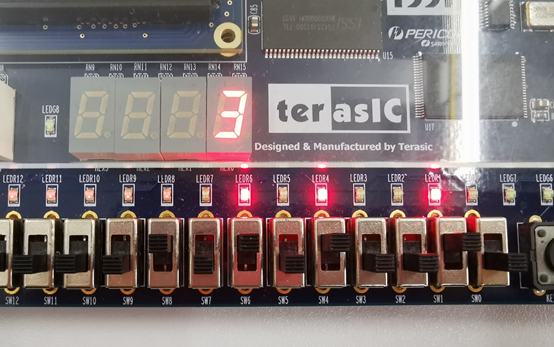

实验测试

开发板引脚分配

引脚绑定设置如下:

联机调试

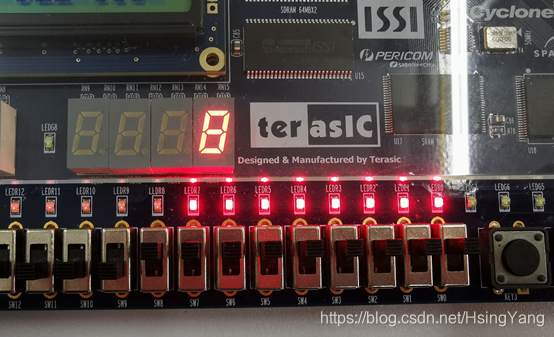

① 使能端Enable未启动(SW8为0)

此时,所有器件不工作:

② 使能端Enable启动(SW8为1)

如下面两图所示,7端数码管HEX0可以根据正确显示:SW0-SW7的对应故障个数:

总结

通过本次课程设计,掌握了有关同步时序电路的知识,了解了同步时序电路的基本设计步骤,并同通过这些知识设计出了基于时序电路的计数器,完成了数字电子钟的仿真设计。

通过本次课程设计,掌握了Verilog语言的基本特征,学习了always、if、case等语句。结合Altera ED2-115开发版,通过Verilog语言进行编程,最终实现了一个路灯巡回检测器。